# Scaling of High-Aspect-Ratio Current Limiters for the Individual Ballasting of Large Arrays of Field Emitters

Stephen A. Guerrera, *Student Member, IEEE*, Luis Fernando Velásquez-García, *Senior Member, IEEE*, and Akintunde Ibitayo Akinwande, *Fellow, IEEE*

Abstract—We report the fabrication and characterization of high-aspect-ratio silicon pillar current limiters [vertical ungated field-effect transistors (FETs)] for ballasting individual field emitters within field-emitter arrays (FEAs). Dense (1- $\mu$ m pitch) FEAs that are individually ballasted by 100-nm-diameter and 10- $\mu$ m-tall current limiters were fabricated, resulting in an emitter tip radius under 10 nm. When characterized without field emitters, the vertical current limiters (ungated FETs) show current-source-like behavior, with saturation currents up to 15 pA/FET. When the current limiters are incorporated into large arrays of field emitters, the current–voltage characteristics of the FEA show evidence of current limitation at high extraction gate voltages. Emission current densities of over 200  $\mu$ A/cm<sup>2</sup> were obtained from 1.36 million emitter arrays with 5- $\mu$ m pitch.

*Index Terms*—Ballasting, cathodes, electron supply control, Si field-emission arrays, vertical ungated Si field-effect transistors (FETs).

### I. INTRODUCTION

**F** IELD-EMITTER ARRAYs (FEAs) are excellent cold cathodes; however, they have not found widespread adoption in demanding device applications because of several major challenges, the most significant of which is spatial and temporal nonuniformities. Spatial nonuniformities typically result from variations in emitter tip radius, and since all FEAs have nonzero tip radius distribution [1], subutilization of the array elements often results. For example, sharper emitters burn out from Joule heating before duller emitters turn on reducing the overall current density and the total emission current attainable from FEAs.

To address these nonuniformities, researchers have incorporated current-limiting (ballasting) elements such as large resistors [2] and MOSFETs [3], [4] into FEAs; however, neither

S. A. Guerrera and A. I. Akinwande are with the Department of Electrical Engineering and Computer Science, Massachusetts Institute of Technology, Cambridge, MA 02139 USA (e-mail: guerrera@mit.edu; akinwand@ mtl.mit.edu).

L. F. Velásquez-García is with the Microsystems Technology Laboratories, Massachusetts Institute of Technology, Cambridge, MA 02139 USA (e-mail: lfvelasq@mit.edu).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TED.2012.2204262

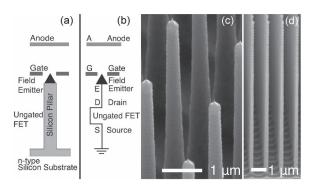

Fig. 1. (a) Schematic diagram of a single field emitter ballasted by an ungated FET. (b) Circuit diagram of the FET–FEA structure. (c) SEM image of the completed FET–FEA structure. (d) Cross-sectional SEM image of an ungated FET current limiter without a field emitter with oxide removed to show the pillar.

of these solutions simultaneously provide high emitter density, high current density, and high current. A robust solution of the uniformity problem requires individual control of each field emitter by a suitable ballasting element. Several researchers have demonstrated a Si tip-on-Si pillar structure [5]–[8]; how-ever, only Velásquez-García *et al.* used the Si pillar as a current limiter to improve uniformity [8]. The work reported in [5] and [6] used the Si post to decrease the capacitance between the gate and the substrate to allow higher frequency operation, while Takemura *et al.* [7] used the pillar to improve reliability.

In Fig. 1, a schematic drawing [Fig. 1(a)] and equivalent circuit diagram [Fig. 1(b)] of the FEA and current-limiting device are shown. The vertical current limiter (ungated FET) has a current-source-like I-V characteristic when biased at voltages larger than its saturation voltage [9], [10]. To limit the emission current, the vertical ungated FET uses pinchoff and velocity saturation of majority carriers at high fields in a high-aspect-ratio silicon channel.

When vertical current limiters are connected in series with individual field emitters, they limit the current from each field emitter in the array, allowing for uniform emission without thermal runaway or burnout, provided that their saturation current is below the burnout limit [8], [11]. This current limitation is consistent with the operation of the device in the electron-supply-controlled regime instead of the electron-transmission-controlled regime as observed by Ding *et al.* for Si FEAs [4], [12] allowing for reliable operation of FEAs at high currents.

Manuscript received January 25, 2012; revised May 8, 2012 and May 31, 2012; accepted June 5, 2012. Date of current version August 17, 2012. This work was supported in part by DARPA/MTO under the HiFIVE program (Program Manager Mark Rosker) under Grant W911NF-08-1-0098. The review of this paper was arranged by Editor M. Thumm.

The combined vertical ungated FET–FEAs reported by Velásquez-García *et al.* in [13] had Si pillars with a diameter of 1  $\mu$ m, a height of 100  $\mu$ m, and 10- $\mu$ m pitch, resulting in a density of 10<sup>6</sup> tips/cm<sup>2</sup>. The FEAs are capable of high and uniform current emission (0.5 A and 0.5 A/cm<sup>2</sup>). With an integrated self-aligned gate, the devices should have a gate aperture roughly equal to the Si pillar diameter [14], resulting in turn-on voltages of approximately 25 V and operating voltages of 75–100 V [1].

Reducing all of the dimensions of the current limiter–FEA structure provides several benefits. By shrinking the pitch of the emitters, the tip density is increased. Because the pillar cross-sectional area is smaller, the saturation current for a given doping density is lower; however, by increasing the doping in the pillar, the current density increases, allowing the same current per emitter to be obtained from narrower pillars. In addition, the gate aperture scales with the pillar diameter. Thus, by decreasing the pillar diameter—and, by implication, the gate aperture—the field factor  $\beta$  (cm<sup>-1</sup>), which relates the gate voltage to the electrostatic field at the tip surface, increases, resulting in lower turn-on and operating voltages. In practice, Pflug *et al.* demonstrated gate apertures as small as 70 nm, resulting in a turn-on voltage of 8.5 V [15].

A consequence of using vertical ungated FETs to limit the current from FEAs is the larger energy spread of the emitted electrons when compared to unballasted FEAs. In an unballasted FEA, each emitter in the array has the same gate-emitter voltage bias. However, when a vertical ungated FET current limiter controls the current through each emitter, the gate voltage  $V_G$  is divided between the gate–emitter voltage  $V_{GE}$ and the drain-source voltage  $V_{\rm DS}$  of the vertical current limiter, i.e.,  $V_G = V_{GE} + V_{DS}$ . Because each emitter is biased at a different gate-emitter voltage, electrons from each emitter are accelerated by different voltages, resulting in a wider energy distribution. The energy spread of the FEA current can be reduced by shrinking the gate aperture, and thus increasing  $\beta$ , while keeping its uniformity constant. Using a FEM simulation platform, we estimated that, by increasing  $\beta$  by a factor of five while keeping the same tip radius statistics, the energy spread across the FEA decreased from 5 to 2 eV.

To obtain FEAs with higher current densities, lower operating voltages, and reduced energy spread while retaining current uniformity, we expanded on the work of Velásquez-García *et al.* by decreasing the diameter and pitch of their tip-on-Si pillar structure by an order of magnitude while keeping the same aspect ratio. We have fabricated scaled current limiter/FEAs with 1- $\mu$ m pitch, 100-nm diameter, and 10- $\mu$ m pillar height [Fig. 1(c)]. However, we were unable to test them using a suspended extraction gate, as electric field screening from nearby pillars rendered it impossible to obtain a sufficiently high field factor. Two-dimensional electrostatic simulations indicate that, at 1- $\mu$ m pitch, an extraction gate voltage in excess of 10 kV is required for field emission without a proximal gate. This voltage exceeds the dielectric strength of the polymer spacer used in our field-emission testing apparatus.

Thus, the focus of this paper is on the following: 1) the fabrication and characterization of vertical ungated FET current limiters that are 100 nm in diameter and 8  $\mu$ m tall and have

$1-\mu m$  pitch, resulting in a density of  $10^8 \text{ cm}^{-2}$ , and 2) the fabrication and characterization of FEAs individually ballasted by vertical ungated FET current limiters that are 10  $\mu m$  tall and have a pitch of 5  $\mu m$ .

## II. SIMULATION OF VERTICAL CURRENT LIMITERS

To estimate the performance of the vertical ungated FET current limiters and serve as a guide to their fabrication, extensive process and device simulations were performed using the SILVACO toolset (Silvaco International, Santa Clara, CA). For these simulations, the Si pillar cross-sectional area was fixed at 100 nm  $\times$  100 nm. The area surrounding the pillar was filled with SiO<sub>2</sub>, and both the top drain contact and substrate source contact were assumed to be perfect ohmic contacts. No interface states or fixed charge at the Si–SiO<sub>2</sub> interface was included in these simulations.

Once the structure was obtained, ATLAS was used to simulate the current–voltage characteristics of a single vertical ungated FET current limiter. These simulations solved Poisson's equation self-consistently with the carrier flow and continuity equations. To explore the functional dependences on channel length and doping, the doping density  $N_D$  was varied between  $10^{13}$  and  $10^{16}$  cm<sup>-3</sup>, and the channel length L was varied between 1 and 10  $\mu$ m. For the simulations where  $N_D$  was varied, the channel length was fixed at  $10 \ \mu$ m, and for the simulations where L was varied,  $N_D$  was fixed at  $5 \times 10^{14}$  cm<sup>-3</sup>.

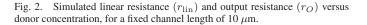

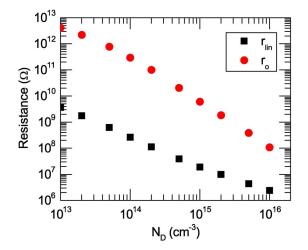

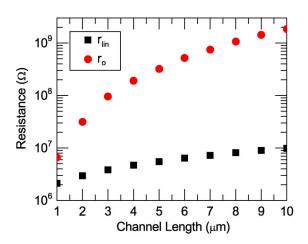

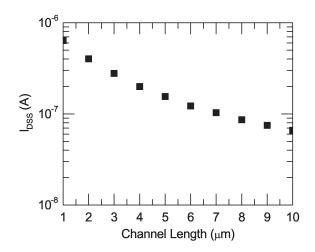

The linear resistance  $(r_{\rm lin})$ , the output resistance,  $(r_o)$ , and the drain saturation current per pillar  $(I_{\rm DSS})$  were extracted from the simulations. The dependences of  $r_o$  and  $r_{\rm lin}$  (Fig. 2) and  $I_{\rm DSS}$  (Fig. 3) on the doping density are plotted in Figs. 2 and 3. In Figs. 4 and 5, the dependences of  $r_o$  and  $r_{\rm lin}$ (Fig. 4) and  $I_{\rm DSS}$  (Fig. 5) on the channel length are shown. An aspect ratio greater than 50:1 is required to obtain a sufficiently large dynamic resistance while simultaneously providing the large current per tip required for high-performance FEAs. We followed the sensitivity analysis approach originally proposed by Hong and Akinwande [4] and adopted by Velásquez-García *et al.* [8] to determine the dynamic resistance  $(r_o = 10^{11} \Omega)$  required for uniform emission current.

Fig. 3. Simulated drain saturation current ( $I_{\rm DSS}$ ) versus donor concentration for a fixed channel length of 10  $\mu$ m.

Fig. 4. Simulated  $r_{\rm lin}$  and  $r_O$  versus channel length, for a fixed  $N_D$  of 5  $\times$   $10^{14}~{\rm cm}^{-3}.$

Fig. 5. Simulated  $I_{\rm DSS}$  versus channel length for a fixed  $N_D$  of  $5 \times 10^{14} {\rm ~cm^{-3}}$ .

Increasing the aspect ratio much beyond 100:1, however, gives diminishing returns, with all three parameters approaching asymptotic values. In addition, current limiters with aspect ratios larger than 100:1 further complicate fabrication. Based on these simulations, wafers with a doping density of  $2 \times$

$10^{14}$  cm<sup>-3</sup> and a target pillar height of 10  $\mu$ m (corresponding to a pillar aspect ratio of 100:1) were chosen to theoretically obtain devices with a saturation current of 1 nA/pillar and an output resistance greater than  $10^{11} \Omega$ .

#### **III. FABRICATION OF VERTICAL CURRENT LIMITERS**

Large arrays  $(3.6 \times 10^7 \text{ devices})$  of vertical current limiters without field emitters were fabricated using 6-in n-Si wafers. First, a 0.3- $\mu$ m thermal SiO<sub>2</sub> hardmask is grown. Using an i-line wafer stepper, photolithography is performed to create photoresist dots approximately 500 nm in diameter with 1- $\mu$ m pitch. These dots are used to pattern the oxide film in a  $CF_4/CHF_3/Ar$  reactive ion etcher (RIE). The vertical current limiters are next etched using a Bosch process deep RIE (DRIE). Following this step, the photoresist and any polymers remaining from the passivation step of the DRIE are etched (ashed), and the oxide is removed in 50% HF. An RCA clean is performed, and a thermal oxide film is grown both to passivate and smooth the silicon pillar surface and to further reduce the dimensions of the pillar. Fig. 1(d) shows a cross-sectional SEM image of the vertical current limiters after this oxidationthinning step with the oxide removed, demonstrating a pillar diameter of 93 nm at the thinnest point.

To make top contact to the pillars, the remaining gaps between the pillars are filled in with dielectric. A 600-nm-thick LPCVD low-temperature oxide is deposited, and then, 0.5  $\mu$ m of undoped poly-Si is deposited using LPCVD to fill in the remaining gaps. Then, 75% of the poly-Si on the surface is removed through oxidation and subsequent etching in HF, and contact windows to the vertical current limiters are opened using RIE after the remaining poly-Si is oxidized.

Finally, a shallow ion implantation of arsenic was performed, annealed, and activated at 950 °C in an N<sub>2</sub> ambient. Then, a metal stack consisting of a 100-nm TiN diffusion barrier and 1- $\mu$ m Al was sputtered to form ohmic contacts to Si. The metallization was patterned using photolithography and Cl<sub>2</sub> plasma, and the metallization was annealed at 400 °C under forming gas.

### IV. *I–V* CHARACTERIZATION AND ANALYSIS OF SCALED VERTICAL CURRENT LIMITERS

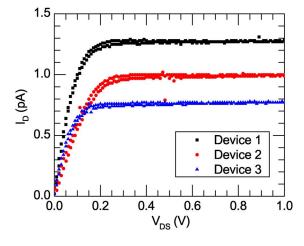

I-V characterization took place in a probe station using an Agilent 4156C semiconductor parameter analyzer. During the measurement, the substrate (and the source end of the channel) was held at 0 V, and a positive voltage  $V_{\rm DS}$  was applied to the drain contact. Table I is a summary of experimental I-Vmeasurements performed. In general, the devices demonstrate current saturation, with a saturation current  $(I_{DSS})$  of approximately 15 pA/pillar and an output conductance  $(g_{lin})$  less than  $1.8 \times 10^{-13}$  S/pillar. The current saturates at a drain-to-source saturation voltage  $(V_{\rm DSS})$  under 0.2 V. A linear conductance  $(g_{\rm lin})$  of up to  $2.6 \times 10^{-10}$  S/pillar was measured. To ensure that the resistance was not a direct result of contact resistance, transfer length measurements (TLMs) were performed. From the TLM structures, a specific contact resistance of  $3.2 \times$  $10^{-3} \ \Omega/cm^2$  was obtained, resulting in an estimated contact resistance of  $3.80 \times 10^7 \Omega$  to the pillar, which is several orders

| Size of Array | I <sub>DSS</sub> /pillar<br>[pA] | V <sub>DSS</sub><br>[V] | <i>g<sub>tin</sub>/</i> pillar<br>[pS] | <i>g<sub>out</sub>/</i> pillar<br>[pS] |

|---------------|----------------------------------|-------------------------|----------------------------------------|----------------------------------------|

| 1             | 8.5                              | 0.06                    | 150                                    | 0.33                                   |

| 4             | 0.50                             | 0.20                    | 6.7                                    | 0.18                                   |

| 5             | 1.3                              | 0.20                    | 12                                     | 0.061                                  |

| 8             | 2.2                              | 0.80                    | 28                                     | 0.096                                  |

| 62.5k         | 2.6                              | 0.01                    | 23                                     | _ <sup>a</sup>                         |

| 125k          | 1.8                              | 0.08                    | 22                                     | -                                      |

| 250k          | 1.9                              | 0.06                    | 33                                     | -                                      |

| 500k          | 2.1                              | 0.06                    | 38                                     | 0.0060                                 |

| 1M            | 15                               | 0.15                    | 250                                    | 0.090                                  |

| 2M            | 10                               | 0.08                    | 42                                     | 0.022                                  |

| 4M            | 4.7                              | 0.05                    | 99                                     | 0.0065                                 |

TABLE I MEASURED CURRENT–VOLTAGE CHARACTERIZATION DATA

a. Indicates negative resistance in the saturation regime

Fig. 6. I-V characteristics of three different single vertical current limiters on a single die exhibiting process and/or doping variation.

of magnitude less than the linear resistance. The aforementioned extraction of contact resistance likely underestimates the contact resistance to the pillars, as the contact openings in the TLM test structures were 300  $\mu$ m  $\times$  10  $\mu$ m, whereas the pillar cross section is 100 nm  $\times$  100 nm.

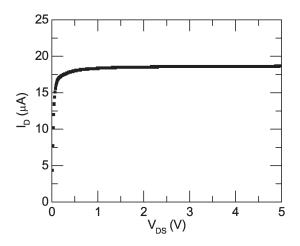

Fig. 6 shows the I-V characteristics for several single current limiters in a single array, and Fig. 7 shows an I-Vcharacteristic for an array of 4M current limiters. In both cases, the I-V characteristic provides evidence for the currentlimiting capabilities of the scaled current limiter structure. Our simulation results predicted that the saturation current, output conductance, and linear conductance should have been a factor of 30 larger than what was extracted from I-V characterization of the fabricated devices. We do not have a specific explanation for the discrepancy between the device simulation and our measurements. We speculate that this discrepancy could be primarily caused by the low doping in the channel. With a doping density of  $2 \times 10^{14}$  cm<sup>-3</sup>, assuming a Poisson distribution of dopant atoms, there are approximately 35 donor atoms in the entire 10- $\mu$ m-long channel. Because of the small number of dopant atoms, we expect random dopant fluctuations (RDFs) and interface traps at the Si/SiO2 interface to have an impact on the vertical silicon ungated FET current limiters. While RDF and interface traps typically manifest themselves as threshold voltage shifts in MOS devices [16]-[18], in the

Fig. 7. I-V characteristic of an array of 4M vertical current limiters.

vertical current limiter, RDF and interface traps directly affect the channel conductivity and, in large part, explain the variation of saturation currents and linear conductivities measured in the actual devices. For a particular doping density and pillar diameter, simulations suggest that it is possible to pinch off the channel even when there is no applied voltage given a sufficiently high interface trap density. This results in much reduced drain currents. These deleterious effects could be substantially curtailed if the doping density is increased to at least  $1 \times 10^{15}$  cm<sup>-3</sup>. Another source of conductivity variation is pillar diameter variation, arising from nonuniformities in fabrication, particularly in the photolithography and etching steps.

## V. THERMAL RUNAWAY AND FAILURE ANALYSIS OF VERTICAL CURRENT LIMITERS

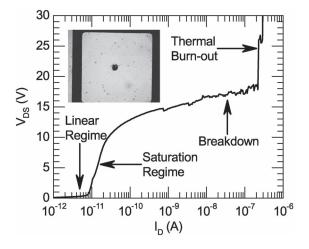

To explore the ultimate performance and failure mode of the current limiters, an analysis of the thermal breakdown of the silicon pillars was performed. Experiments were conducted to verify the maximum possible current sourced before failure of the vertical current limiters. Several single vertical current limiters were characterized using an Agilent 4156C semiconductor parameter analyzer under conditions where current was varied and voltage was measured until thermal runaway and device failure occurred. Fig. 8 shows a representative voltage-current characteristic, which exemplifies the failure that occurred. I-Vcharacteristics of the device were taken before and after stressing. Before stressing, the device had a saturation current of 8 pA. At a bias current of 11 pA, impact ionization in the high-field region of the channel was observed, resulting in a large change in current with small increase in voltage. At a current level of 200 nA, the device failed, and the measured voltage reached the testing compliance limit, indicating that an open circuit has formed. The inset of Fig. 8 shows an optical micrograph of the metal contact pad after stressing, showing physical damage resulting from the destructive testing: a large crater in the metallization centered on the location of the single pillar contact.

Following the analysis of the thermal limits of field emitters presented by Utsumi in [11], the maximum current density at

Fig. 8. Voltage–current stressing sweep resulting in thermal runaway and breakdown. Breakdown occurred at  $2 \times 10^{-7}$  A. (Inset) After stressing, there is visible damage to the metallization.

burnout due to Joule heating approximated by

$$J_{\max} = \frac{\sqrt{2T_m \tilde{\sigma} k}}{h} (A/cm^2) \tag{1}$$

where h is the height of the structure,  $T_m$  is the melting temperature of silicon,  $\tilde{\sigma}$  is the average value of electrical conductivity, taken between room temperature and  $T_m$ , and k is the thermal conductivity of silicon. Using the thermal conductivity and electrical conductivity values for n-type silicon with a donor concentration of  $2 \times 10^{14}$  cm<sup>-3</sup>, a value of 100 nA for  $I_{\text{max}}(I_{\text{max}} = J_{\text{max}} \times \text{cross-sectional area})$  is obtained for a 100-nm-diameter column, agreeing with the experimental value of 200 nA to within a factor of two.

## VI. FABRICATION OF FEAs INDIVIDUALLY BALLASTED BY VERTICAL CURRENT LIMITERS

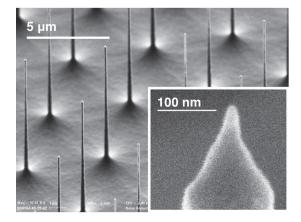

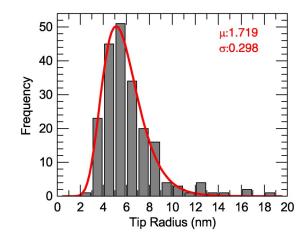

The combined ungated FET current limiter-FEA structure was fabricated with 5- $\mu$ m pitch and hexagonal packing. The fabrication begins identically to the vertical current limiter structure described in Section III. After the patterning of the oxide in the RIE tool, the initial formation of the emitter cones is performed using RIE with  $SF_6/O_2$  chemistry. The partial pressure of oxygen changes the lateral etch rate while barely changing vertical etch rate, allowing for control over the etch. The undercutting step needed to be precisely controlled to obtain a sharp tip after the oxidation to reduce the pillar diameter. After the tip formation, the pillar is etched using the same DRIE process as in the vertical current limiter process. Following the DRIE step, the structure was oxidized at 1000 °C using dry O<sub>2</sub> to simultaneously form sharp emitter tips while reducing the pillar diameter. Finally, the thermally grown oxide is removed using 10:1 diluted HF. A SEM image of the completed structure is shown in Fig. 9. The pillars are 10  $\mu$ m tall, with a diameter of 110 nm and a tip radius under 10 nm. Fig. 9 shows a SEM image of the complete FEA structure after field-emission testing. Fig. 10 is a plot of the radii of 209 tips. The statistics follow a log-normal distribution with a mean of 5.6 nm and a standard deviation of 1.3 nm. The tip radius measurements were made using SEM images taken after the

Fig. 9. SEM micrograph of the completed structure. The pillars are 10  $\mu$ m tall, are 100 nm in diameter, and have an emitter tip radius under 10 nm. (Inset) Detail of a representative emitter tip.

Fig. 10. Radii of 209 field emitters measured using SEM across the die after field-emission testing. The distribution is log normal with a mean of 5.6 nm and a standard deviation of 1.3 nm.

device characterization; hence, they are representative of the actual device dimensions.

## VII. *I–V* Characterization of FEAs Individually Ballasted by Vertical Current Limiters

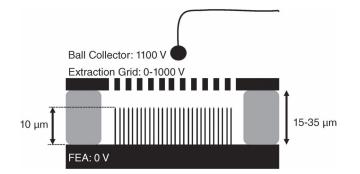

Arrays of 1.36 million emitters were fabricated following the process described in Section VI using n-type Si wafers with a nominal donor concentration of  $2 \times 10^{14}$  cm<sup>-3</sup>. The experimental setup is shown in Fig. 11. A  $25 \pm 10$ - $\mu$ m-thick nylon spacer was used to insulate the emitters from an unaligned perforated extraction grid, resulting in a tip-grid distance of 5–25  $\mu$ m. When electrons are emitted from the sample, a fraction of the electrons pass through the grid and are collected by a suspended ball-shaped anode biased at +1100 V, allowing us to determine whether the source of the current is leakage through the dielectric spacer or electron field-emission current. The linear relationship between the current collected at the grid and the suspended anode suggests that the origin was field emission. At higher voltages, this linearity does not hold. It is likely that the polymer spacer is beginning to break down at these voltages, resulting in significant leakage current in addition to the field-emission current.

Fig. 11. Schematic of the triode configuration used to test the ballasted FEAs. A nylon polymer gasket acts as a standoff between the FEA and the extraction gate.

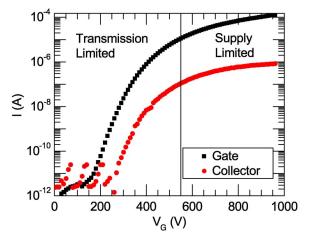

Fig. 12. I-V characteristics for an array of 1.36 million individually ballasted field emitters. At gate voltages over 550 V, the FEA enters a regime where the current is limited by the supply of electrons to the field emitters by the vertical current limiter, rather than the transmission through the barrier.

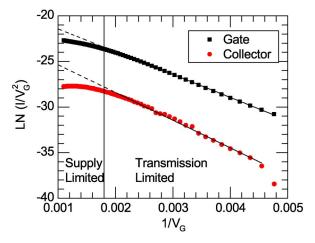

I-V characterization took place in an ultra-high vacuum testing chamber at a pressure of  $9 \times 10^{-10}$  torr using three commercially available high-voltage source measure units (SMUs) (Keithley model 237 SMUs). Fig. 12 shows the typical I-Vcharacteristics of a 1.36 million tip FEA for electrons collected by both the extraction gate and the anode. The transparency of the extraction gate was about 1%. The Fowler–Nordheim (F–N) plot, shown in Fig. 13, is a common technique for plotting fieldemission data. Ideally, there is a linear relationship between the natural log of the current over the square of the gate voltage and the inverse of the gate voltage [19]. At high extraction gate voltages, if the emission current is limited by the vertical current limiters, the F-N plot should deviate from the linear relationship, and the slope should become less negative at higher voltages. At a bias voltage of approximately 600 V, the F-N characteristic in Fig. 13 begins to deviate from its linear characteristics.

The tip radius may be estimated empirically from the slope of the F–N curve  $b_{\rm F-N}$  using

$$\beta = \frac{0.95 \cdot 6.83 \times 10^7 \cdot \phi^{3/2}}{b_{\rm E \ N}} (\rm cm^{-1})$$

(2)

$$r \approx \frac{1}{\beta} (\text{cm})$$

(3)

where  $\beta$  is the field factor in per centimeters,  $\phi$  is the work function barrier in electronvolts, assumed to be 4.05 eV for

Fig. 13. F–N plot for an array of 1.36 million individually ballasted field emitters, demonstrating the different regions of operation.

n-type Si, and r is the emitter tip radius in centimeters. The slope extracted from the F–N gate current characteristic shown in Fig. 13 was 2942, resulting in a  $\beta$  of  $1.80 \times 10^5$  cm<sup>-1</sup> and an r of 55 nm. This result is not consistent with the experimental measured tip radii shown in Fig. 10 and will be examined further hereinafter.

#### VIII. DISCUSSION

The current–voltage characterization of the individually ballasted FEAs presented in the preceding section is consistent with the results obtained by Velásquez-García *et al.* [13] and the characterization of the vertical current limiter pillars without field-emission structures reported in Section IV. Using the data presented in Table I and assuming that the emission current is limited to 10 pA/emitter, the expected array current is 13.6  $\mu$ A. From Fig. 13, at a gate-to-source bias voltage of 550 V, we observe the transition of the F–N plot from the regime where the current is limited by the transmission of electrons through the barrier to a supply-limited regime. The corresponding emission from the FEA is 11.1  $\mu$ A. This result is consistent with our suggestion that the vertical current limiter controls emission current.

We note that the surface of the current limiters reported in Section IV was covered by carefully processed  $SiO_2$ , whereas the surface of the current limiters ballasting the FEAs is covered with thin oxides that are not carefully processed and hence may be affected by a higher interface trap density. This increased trap density may have an impact on the saturation current of the current limiters. However, based on the experimentally obtained saturation characteristics of the ballasted FEAs reported earlier, we do not believe that this had a major impact on the ability to use this structure for the ballasting of field-emission arrays.

The tip radius obtained from the F–N plot does not agree well with the tip radius distribution obtained from SEM measurements. The presence of a thin native oxide could manifest itself as a lower field factor, which translates into an implied higher work function. However, assuming a work function increase from 4.05 to 4.5 eV changes the extracted tip radius by less than 20%. Hence, this is not very likely. A better explanation is that

the models that describe the electrostatics of a microfabricated field emitter with a self-aligned gate that is very close to the tip [20], [21] do not translate well to structures where the gate is perforated and located about 25  $\mu$ m away with tip-to-tip separation of 5  $\mu$ m and an aspect ratio of 100, as we have in this case. Screening of the tip electrostatic field by proximal tips has been suggested in the literature, particularly when the tip-to-tip distance is far less than the tip-to-gate distance [22].

#### IX. CONCLUSION

Arrays of vertical ungated FET current limiters less than 100 nm in diameter with a pitch of 1  $\mu$ m have been fabricated using batch fabrication techniques. Array sizes from single vertical current limiters to 4M vertical current limiters were characterized. These scaled-down silicon pillars exhibited excellent current control, successfully demonstrating the highest density, smallest diameter, and lowest operating voltage for silicon vertical current limiters ever reported. In addition, field-emission arrays individually ballasted by vertical ungated FET current limiters with 5- $\mu$ m pitch were fabricated, demonstrating possible current limitation from the current limiters at current levels of 200  $\mu$ A.

#### ACKNOWLEDGMENT

The authors would like to thank the staff of MIT's Microsystems Technology Laboratories for their help in the fabrication of the structures. The authors would also like to thank E. Huebel for the fabrication of extraction grids.

#### REFERENCES

- M. Ding, G. Sha, and A. I. Akinwande, "Silicon field emission arrays with atomically sharp tips: Turn-on voltage and the effect of tip radius distribution," *IEEE Trans. Electron Devices*, vol. 49, no. 12, pp. 2333– 2342, Dec. 2002.

- [2] P. Vaudaine and R. Meyer, "'Microtips' fluorescent display," in IEDM Tech. Dig., 1991, pp. 197–200.

- [3] J. Itoh, T. Hirano, and S. Kanemaru, "Ultrastable emission from a metal–oxide–semiconductor field-effect transistor-structured Si emitter tip," *Appl. Phys. Lett.*, vol. 69, no. 11, pp. 1577–1578, Sep. 1996.

- [4] C.-Y. Hong and A. I. Akinwande, "Temporal and spatial current stability of smart field emission arrays," *IEEE Trans. Electron Devices*, vol. 52, no. 10, pp. 2323–2328, Oct. 2005.

- [5] D. Temple, C. A. Ball, W. D. Palmer, L. N. Yadon, D. Vellenga, J. Mancusi, G. E. McGuire, and H. F. Gray, "Fabrication of columnbased silicon field emitter arrays for enhanced performance and yield," *J. Vac. Sci. Technol. B, Microelectron. Nanometer Struct.*, vol. 13, no. 1, pp. 150–157, Jan./Feb. 1995.

- [6] L. N. Yadon, D. Temple, W. D. Palmer, C. A. Ball, G. E. McGuire, C.-M. Tang, and T. A. Swyden, "Mini-column silicon field-emitter arrays," *J. Vac. Sci. Technol. B, Microelectron. Nanometer Struct.*, vol. 13, no. 2, pp. 580–584, Mar./Apr. 1995.

- [7] H. Takemura, Y. Tomihari, N. Furutake, F. Matsuno, M. Yoshiki, N. Takada, A. Okamoto, and S. Miyano, "A novel vertical current limiter fabricated with trench forming technology for highly reliable field emitter arrays," in *IEDM Tech. Dig.*, 1997, pp. 709–712.

- [8] L. F. Velásquez-García, S. A. Guerrera, Y. Niu, and A. I. Akinwande, "Uniform high-current cathodes using massive arrays of Si field emitters individually controlled by vertical Si ungated FETs—Part A: Device design and simulation," *IEEE Trans. Electron Devices*, vol. 58, no. 6, pp. 1775–1782, Jun. 2011.

- [9] J. Baek, M. S. Shur, K. W. Lee, and T. Vu, "Current–Voltage characteristics of ungated GaAs FETs," *IEEE Trans. Electron Devices*, vol. ED-32, no. 11, pp. 2426–2430, Nov. 1985.

- [10] H. J. Boll, J. E. Iwersen, and E. W. Perry, "High-speed current limiters," *IEEE Trans. Electron Devices*, vol. ED-13, no. 12, pp. 904–907, Dec. 1966.

- [11] T. Utsumi, "Keynote address—Vacuum microelectronics: What's new and exciting," *IEEE Trans. Electron Devices*, vol. 38, no. 10, pp. 2276–2283, Oct. 1991.

- [12] M. Ding, H. Kim, and A. I. Akinwande, "Highly uniform and low turnon voltage Si field emitter arrays fabricated using chemical mechanical polishing," *IEEE Electron Device Lett.*, vol. 21, no. 2, pp. 66–69, Feb. 2000.

- [13] L. F. Velásquez-García, S. A. Guerrera, Y. Niu, and A. I. Akinwande, "Uniform high-current cathodes using massive arrays of Si field emitters individually controlled by vertical Si ungated FETs—Part B: Device fabrication and characterization," *IEEE Trans. Electron Devices*, vol. 58, no. 6, pp. 1783–1791, Jun. 2011.

- [14] L.-Y. Chen and A. I. Akinwande, "Aperture-collimated double-gated silicon field emitter arrays," *IEEE Trans. Electron Devices*, vol. 54, no. 3, pp. 601–608, Mar. 2007.

- [15] D. G. Pflug, M. Schattenburg, H. I. Smith, and A. I. Akinwande, "Field emitter arrays for low voltage applications with sub 100 nm apertures and 200 nm period," in *IEDM Tech Dig.*, 2001, pp. 8.5.1–8.5.4.

- [16] B. Hoeneisen and C. A. Mead, "Fundamental limitations in microelectronics. I. MOS technology," *Solid State Electron*, vol. 15, no. 7, pp. 819–829, Jul. 1972.

- [17] R. W. Keyes, "The effect of randomness in the distribution of impurity atoms on FET thresholds," *Appl. Phys. A, Mater. Sci. Process*, vol. 8, no. 3, pp. 251–259, Nov. 1975.

- [18] N. Shiono and C. Hashimoto, "Threshold-voltage instability of n-channel MOSFETs under bias-temperature aging," *IEEE Trans. Electron Devices*, vol. ED-29, no. 3, pp. 361–368, Mar. 1982.

- [19] R. Gomer, Field Emission and Field Ionization. New York: Amer. Inst. Phys., 1961, ch. 1.

- [20] G. N. A. van Veen, "Space-charge effects in Spindt-type field emission cathodes," J. Vac. Sci. Technol. B, Microelectron. Nanometer Struct., vol. 12, no. 2, pp. 655–661, Mar./Apr. 1994.

- [21] L. Dvorson, M. Ding, and A. I. Akinwande, "Analytical electrostatic model of silicon conical field emitters—Part 1," *IEEE Trans. Electron Devices*, vol. 48, no. 1, pp. 134–143, Jan. 2001.

- [22] L. Nilsson, O. Groening, C. Emmenegger, O. Kuettel, E. Schaller, L. Schlapbach, H. Kind, J.-M. Bonard, and K. Kern, "Scanning field emission from patterned carbon nanotube films," *Appl. Phys. Lett.*, vol. 76, no. 15, pp. 2071–2073, Apr. 2000.

**Stephen A. Guerrera** (S'07) received the B.S. degree in electrical and computer engineering from Northeastern University, Boston, MA, in 2008 and the S.M. degree in electrical engineering from Massachusetts Institute of Technology, Cambridge, in 2011, where he is currently working toward the Ph.D. degree with a focus on novel field emission devices.

Luis Fernando Velásquez-García (M'09–SM'10) received the M.S. and Ph.D. degrees from the Massachusetts Institute of Technology (MIT), Cambridge.

He is an expert in microelectromechanical systems (MEMS) and vacuum microdevices. Since 2009, he has been a Principal Investigator with the Microsystems Technology Laboratories, MIT.

Akintunde Ibitayo (Tayo) Akinwande (S'81– M'86–SM'04–F'08) received the Ph.D. degree from Stanford University, Stanford, CA.

Since 1995, he has been with MIT, Cambridge. Since 2009, he has been with the Defense Advanced Research Projects Agency, Arlington, VA.